测试背景

存储器件在计算机、服务器、汽车与消费电子产品上可谓无所不在。DDR是当前最常用的存储器设计技术之一,其高速低功耗特性满足了众多消费者的需求。随着传输速度的加快使得DDR的验证难度呈指数上升。

对于硬件设计人员来讲,DDR的高速率非常容易引起一系列信号完整性问题,引发包括时序冲突、协议背离、时钟抖动等问题。一旦出现DDR裕量测试失效之类的问题,会让很多设计者感到头疼,调试过程非常困难。PCB投板后再验证的方式效率低下也增加了很多成本。因此,如果采用前期信号完整性测试的方法来提前判别DDR问题就方便了许多。

原理及类型

DDR接口基本原理

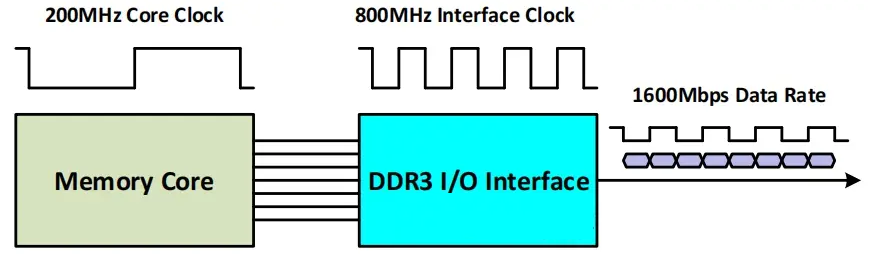

· 内核的频率:100MHz~266MHz,从SDR时代到DDR,再到最新的DDR5;

• 数据速率的提升是通过I/O接口的架构设计实现的,主要有三个技术:

1) 双边沿传输数据:这是DDR名称的来源;

2) 预取技术(Prefetch): 2bit for DDR, 4bit for DDR2, 8bit for DDR3, 8bit for DDR4, 16bit for DDR5…本质上是一个串并转换技术;

3) SSTL/POD Signaling: 克服在高速传输时的信号完整性的问题。

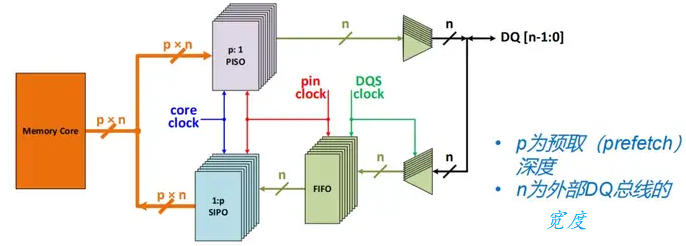

芯片内部的一般架构:保证数据能够高速从芯片引脚输出

在上述这样一种芯片架构中,为了最大程度的降低DRAM芯片的成本,最省成本的方法为:

• 对于读操作,DQS与DQ为边沿对齐;

• 对于写操作,DQS与DQ为中心对齐。

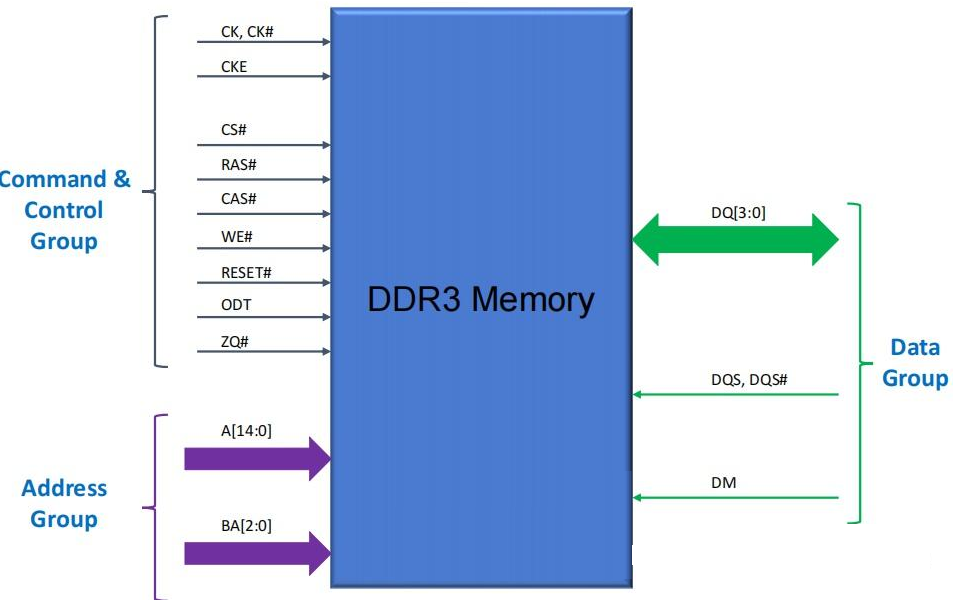

02DDR接口信号分类

引脚框图

测试案例

01 测试设备

No. | Equipment | Model |

1 | Oscilloscope | Tektronix TDS6804B & DPO75902SX |

2 | Probe | Tektronix P7330*1 & Tektronix P7240*2 |

02测试结果

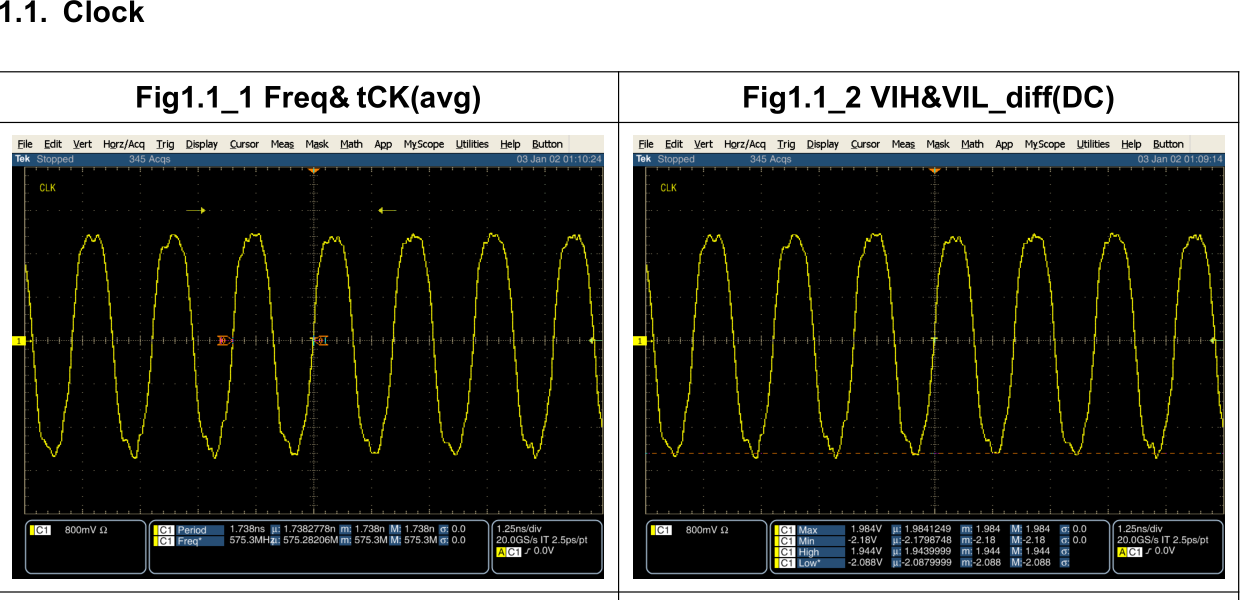

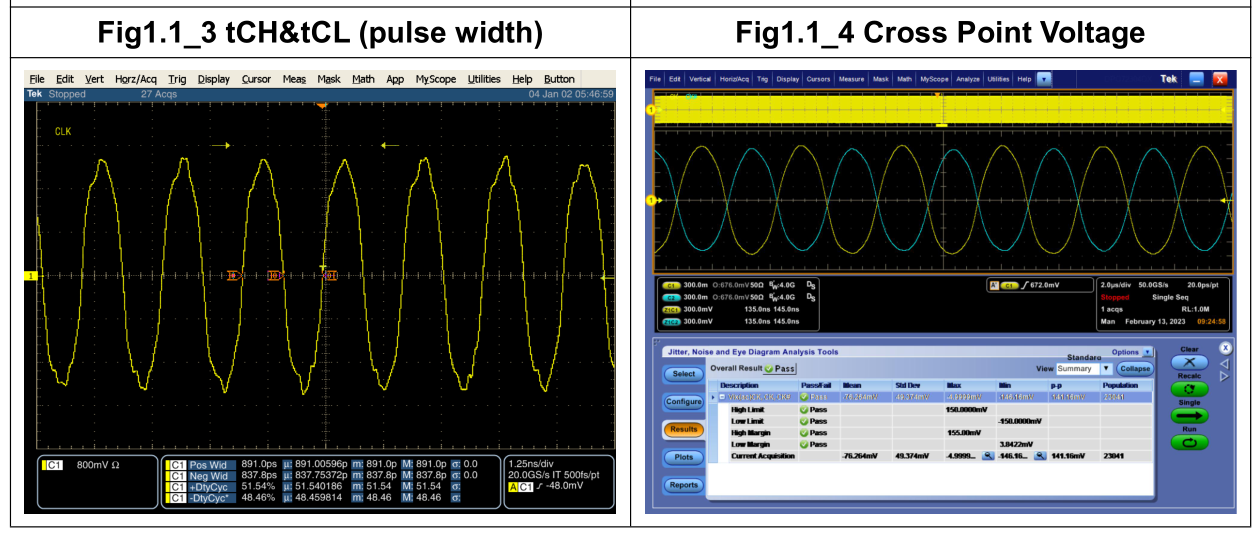

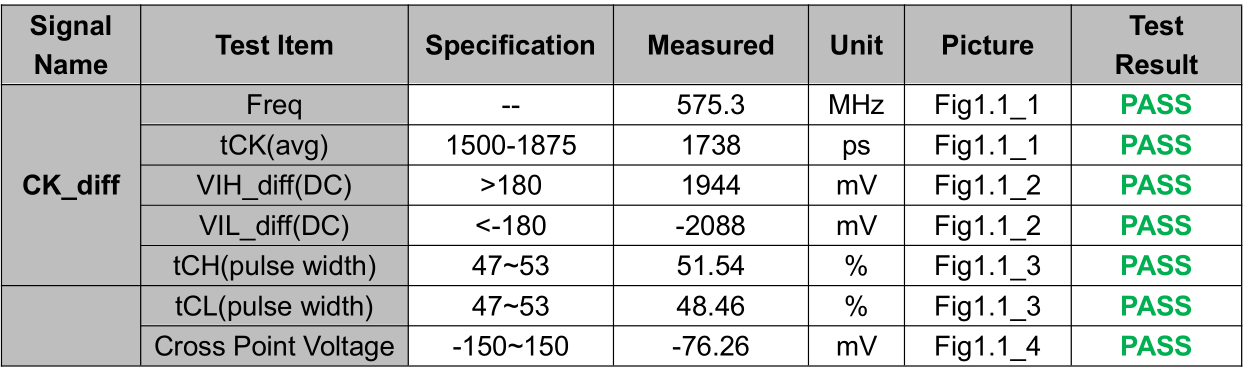

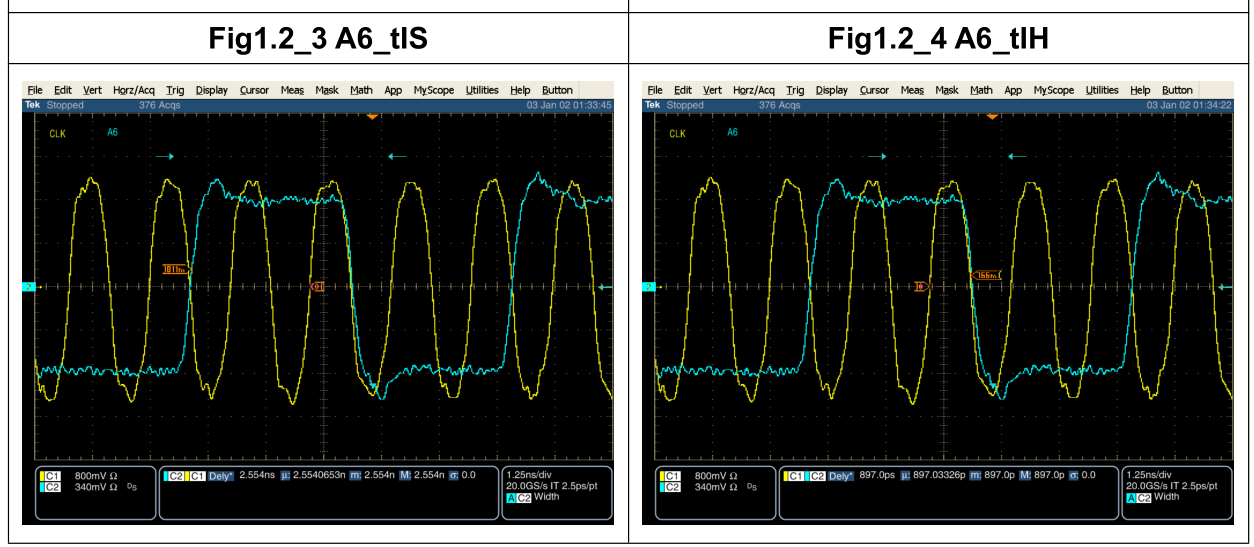

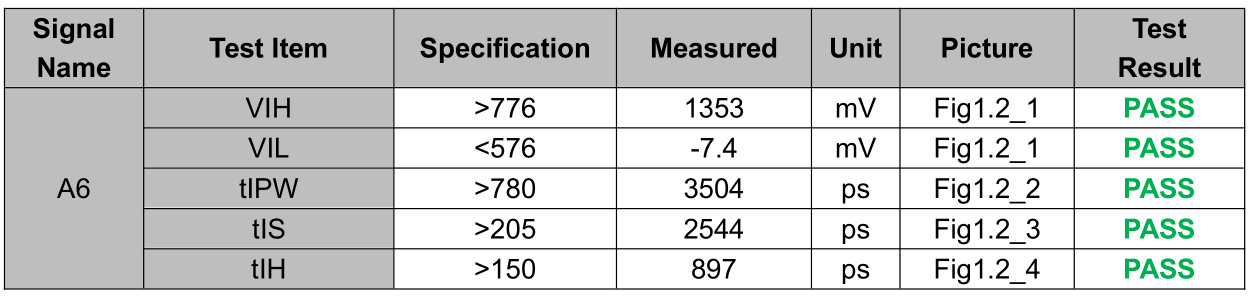

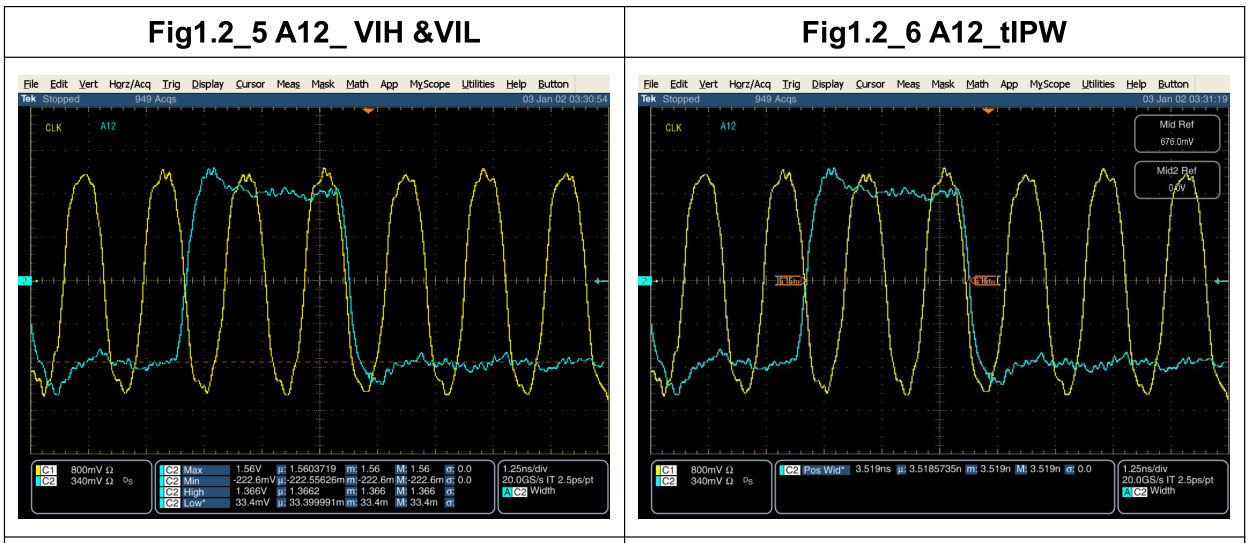

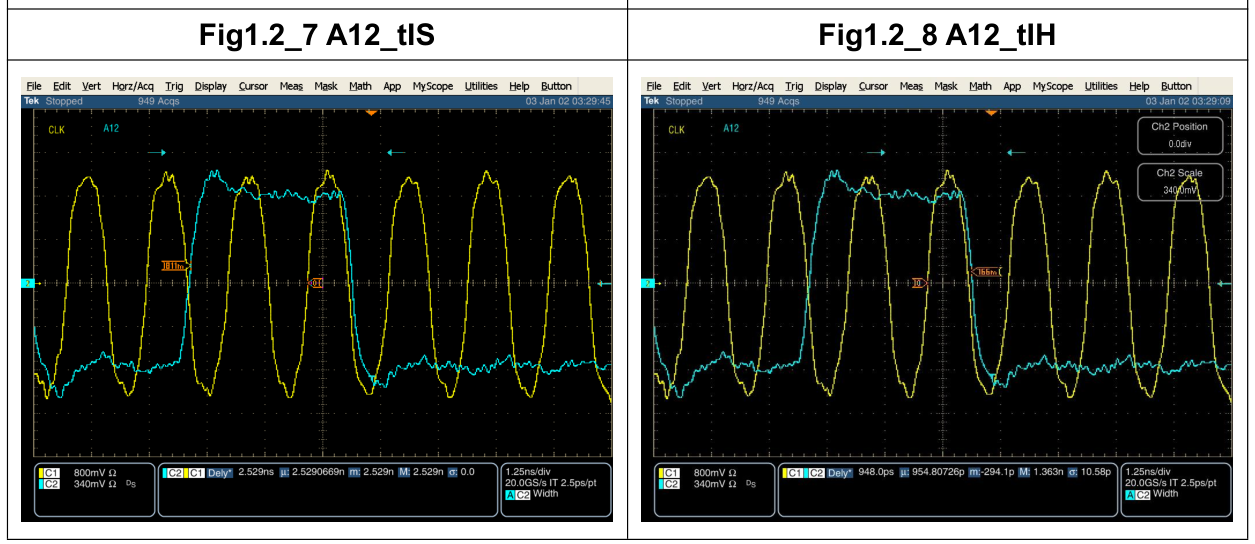

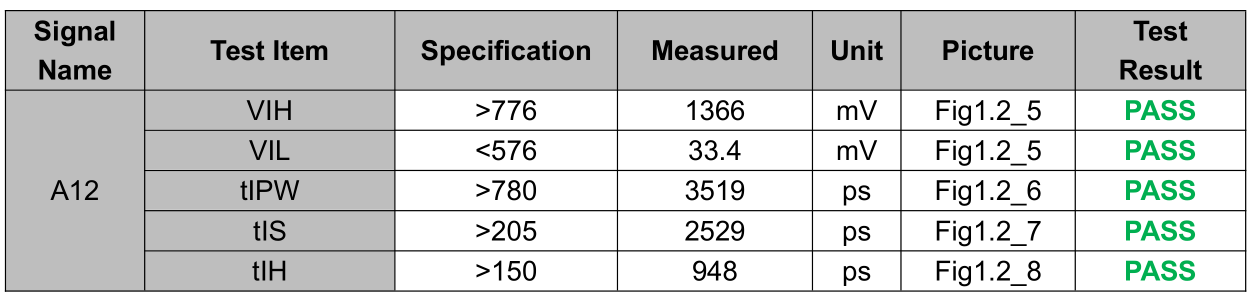

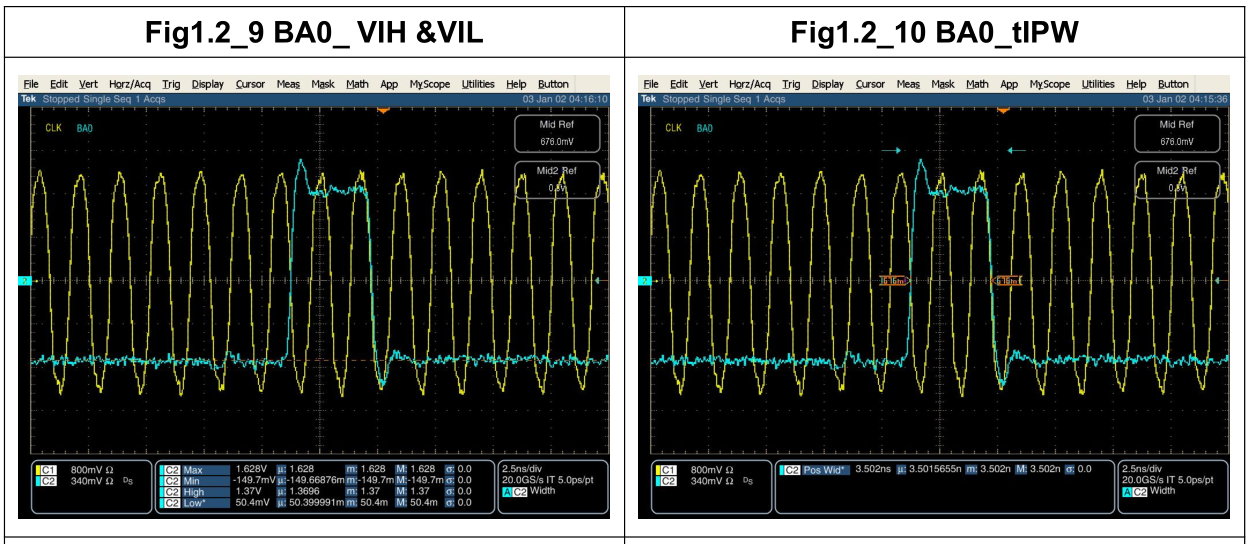

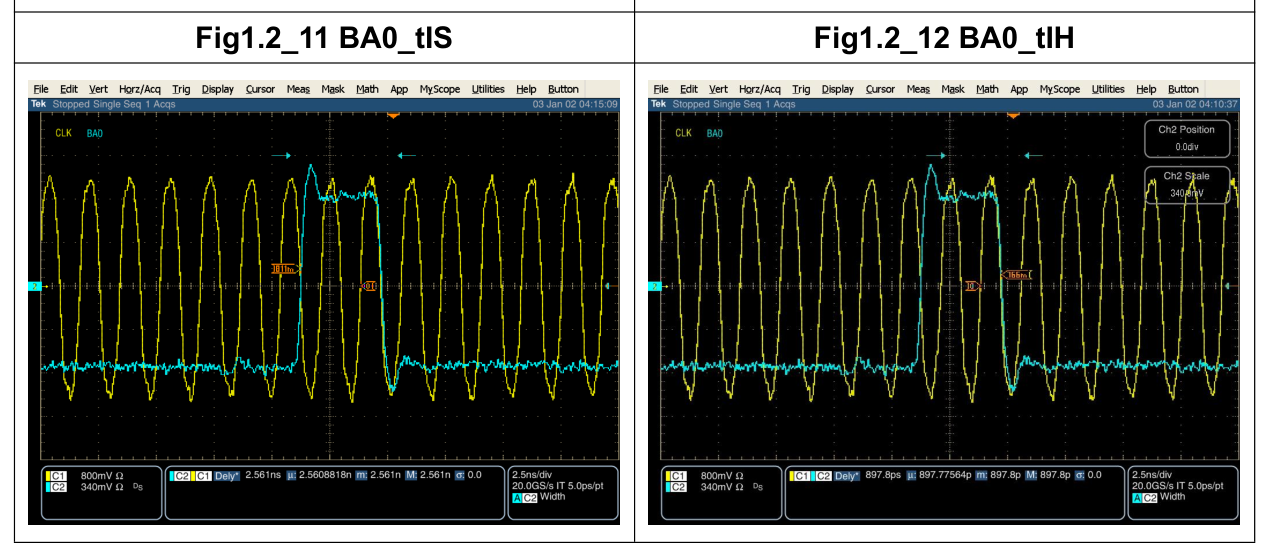

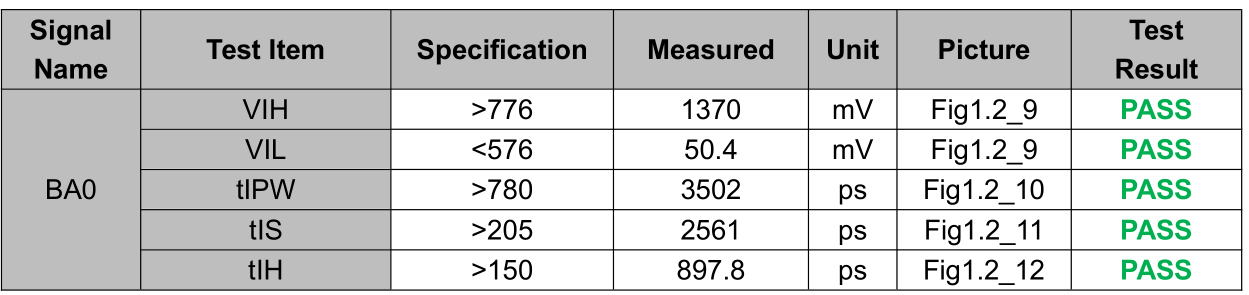

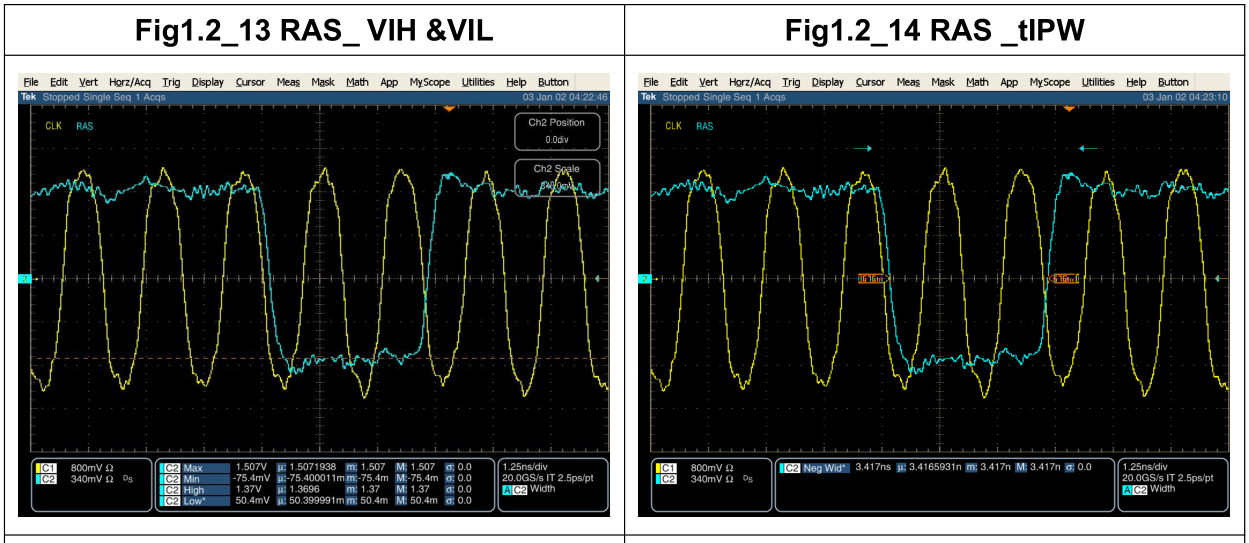

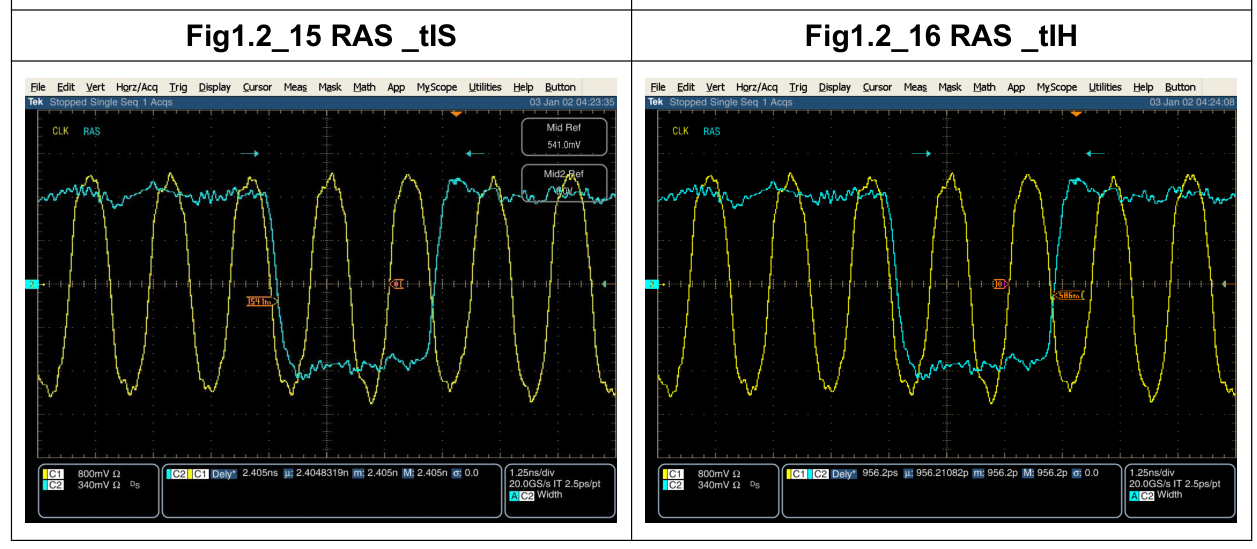

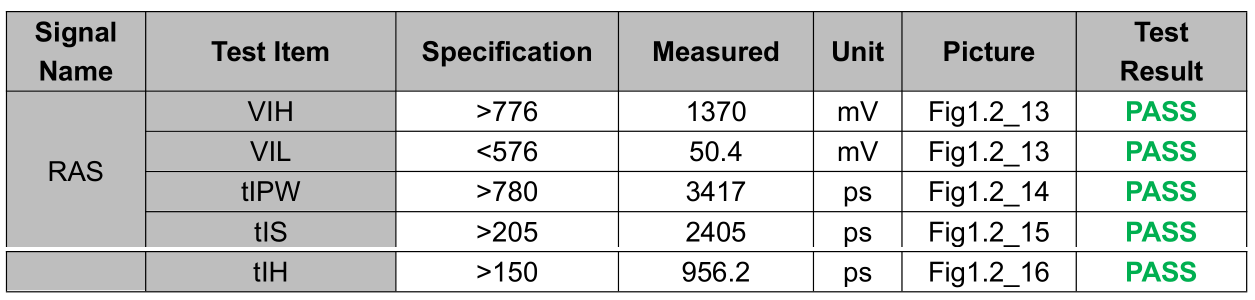

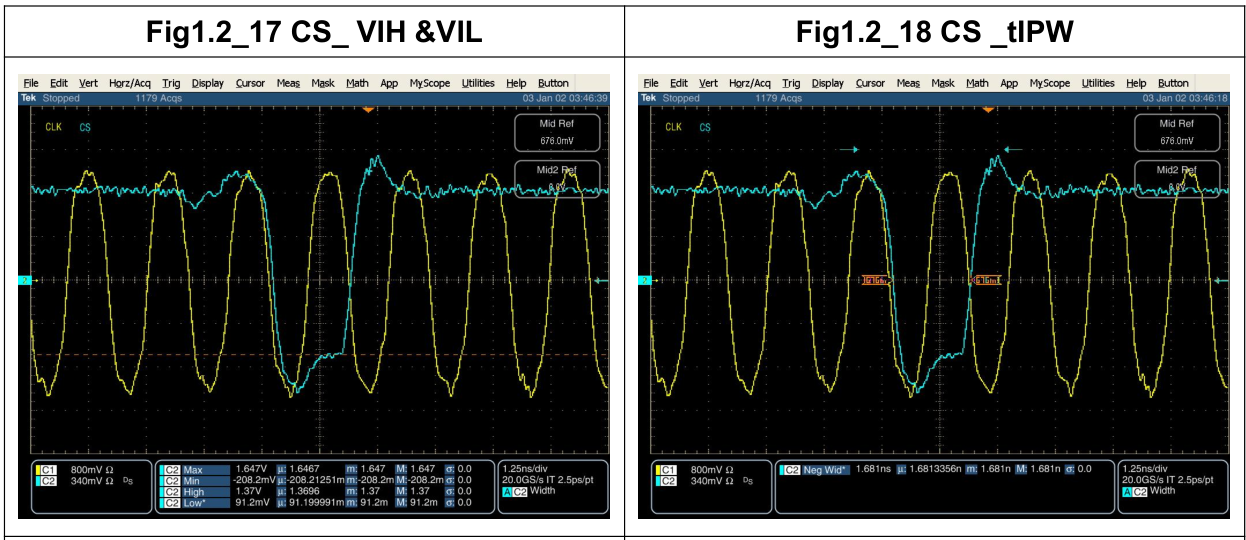

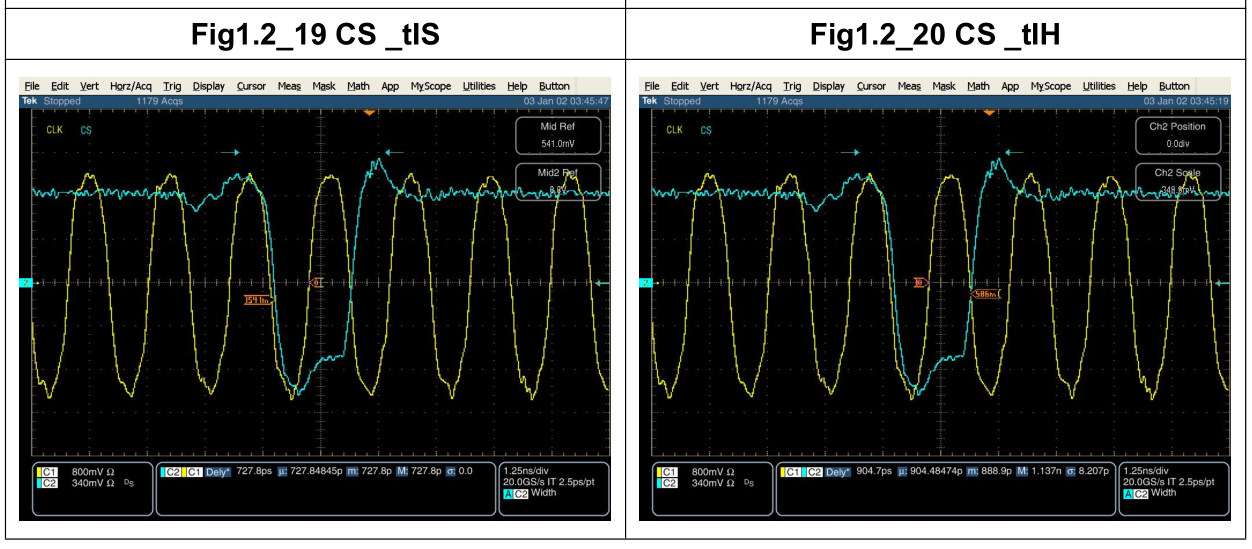

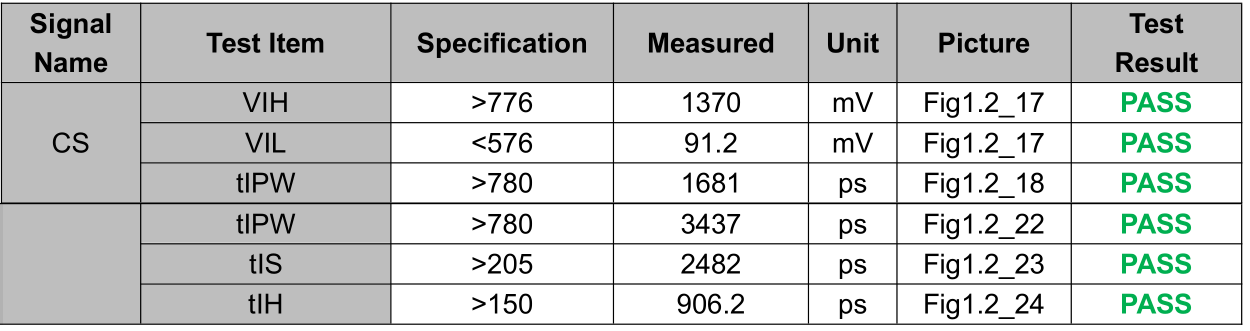

部分测试报告

几乎每一个电子设备,从智能手机到服务器,都使用了某种形式的RAM存储器。尽管闪存NAND继续流行(由于各式各样的消费电子产品的流行),由于SDRAM为相对较低的每比特成本提供了速度和存储很好的结合,SDRAM仍然是大多数计算机以及基于计算机产品的主流存储器技术。

DDR是双数据速率的SDRAM内存,已经成为今天存储器技术的选择。DDR技术不断发展,不断提高速度和容量,同时降低成本,减小功率和存储设备的物理尺寸。在本应用文章中,我们采用针对存储器测试的泰克解决方案,这些方案能够帮助工程师战胜挑战和简化验证过程。可以减少测试时间,并确保最准确的测试结果。

| 具体项目 |